A Peer Revieved Open Access International Journal

www.ijiemr.org

# Implementation of Dual Modulus Prescaler in True Single Phase Clock (TSPC)

\*Ch.Priyanka

\*\*Mr.K.Thirupathi

\*\*\*Mr.M.Devadas

\*M.Tech Dept of E.C.E, Vaagdevi College of Engineering

\*\*Assistant. Prof Dept of E.C.E, Vaagdevi College of Engineering

\*\*\*Assistant. Prof Dept of E.C.E, Vaagdevi College of Engineering

**Abstract** – A high speed CMOS divideby-16/17 dual modulus prescaler has been designed using 250 nm CMOS technology. It consists of the pseudo divide-by- 2/3 prescaler and an asynchronous divide-by-8 prescaler, which are all implemented in TSPC structure. The speed of the divide-by-16/17 dual modulus prescaler is enhanced by decreasing its delay. It is achieved by means of adapting a pseudo divide-by- 2/3 prescaler and by changing the connections between the TSPC D flip-flops. By adapting a pseudo divide-by- 2/3 prescaler and by changing the connection between TSPC D flip-flops, the minimum working period is reduced by about half a NOR gate's delay and by an inverter's delay respectively. The operating frequency is simulated to be up to 5.8 GHz.

Keywords – Dual modulus prescaler, True Single Phase Clock (TSPC), D flip-flops, high speed.

#### I. INTRODUCTION

A prescaler is a counting circuit which is used to reduce a high frequency signal to a lower frequency signal by doing some integer division. The prescaler takes the values in powers of 2 or

some fixed values or some integer value from 1 to 2^P, where P is the number of prescaler bits. Prescalers are widely used at very high frequency to extend the upper frequency range of frequency counters, phase locked loop (PLL) synthesizers, and other counting circuits. When prescaler is used in conjunction with a PLL, it introduces a undesired change between the frequency step size and phase detector

A Peer Revieved Open Access International Journal

www.ijiemr.org

frequency. Therefore, it is necessary to either restrict the integer to a small value or to utilize a dual modulus prescaler. A dual-modulus prescaler is a prescaler that selectively divides the input frequency by one of two integers, such as 16 and 17. When the dual modulus prescaler is implemented in TSPC structure, single clock phase, low power and small area can be obtained. A structure of True Single Phase Clock (TSPC) Dflip- flop is shown in fig.1. The setup time of Fig.1.can be written as

$$T_{\text{setup}} = t_{D\_A}$$

Here tD\_A represents the propagation time from node D to A, which is a clocked inverters

delay. The propagation delay of the TSPC DFF can be written as

$$T_{D_QN} = t_{A_B} + t_{B_QN} T_{D_Q} = t_{A_B} + t_{B_QN} + t_{ON_Q} = t_{ON_Q} + t_{ON_Q}$$

Where TD\_QN and TD\_Q are the propagation delay from clk to QN and Q respectively. tA\_B, tB\_QN , tQN\_ Q represents the propagation delay from node A to B, B to QN, QN to Q respectively. An advantage of TSPC circuit is single clock

phase, low power, small area, large output swing, high robustness and reduction of logic depth. The optimized design is to employ only one AND/OR logic gate before one TSPC DFF. The design rules of TSPC circuits are as

#### follows:

- 1. The AND/OR logic should be embedded in the first stage but not other stages.

- 2. No two paths should control one node to avoid glitches and conflictions.

### II. CONVENTIONAL DIVIDEBY- 16/17 DUAL MODULUS PRESCALER

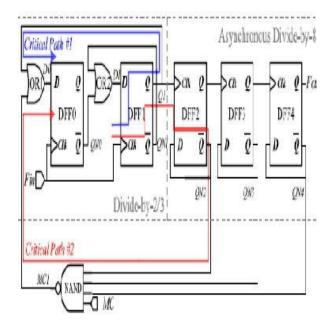

Fig.2. Schematic of conventional divideby-16/17 prescaler

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig.2.shows the schematic of a conventional divide-by-16/17 dual modulus prescaler based on divide-by-2/3 divider. Divide-by-2/3 prescaler is followed by an asynchronous divide-by-8 prescaler which produces the output unction of divide-by-16/17 prescaler. It has two critical paths.

- 1. Critical path #1 comes through DFF1 and OR1.

- 2. Critical path #2 comes through DFF1, DFF2, NAND, OR1 Signals must pass through path #1 within a period of Fin and the signals must pass through path #2 within two periods of Fin. Since OR1 and OR2 gates can be absorbed into the TSPC DFFs, the minimum working period can be written as

$$T_{\min,\text{con}} = \max \left\{ \frac{t_{d-Q,\text{DFFI}} + t'_{\text{setup},\text{DFFO}}}{t_{d-Q,\text{DFFI}} + t_{d,\text{NAND}} + t'_{\text{setup},\text{DFFO}}}}{2} \right.$$

Where td\_ Q, DFF1 represents the propagation delay from clk to Q1 of DFF1. td\_ QN, DFF2 represents the propagation delay from clk to QN2 of DFF2. t'setup,DFF0 represents the setup time of the DFF0 with absorbed OR1 and tD\_NAND is the NAND gate delay.

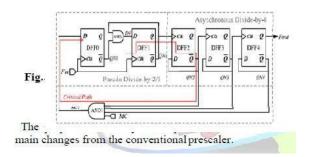

- 1. A new pseudo divide-by-2/3 prescaler is used which accomplish a single but not continuous divide-by-3 operation in a cycle.

- 2. The connections are interchanged between the TSPC D flip flops (i.e., the clk input to the asynchronous divide-by-8 prescaler is given from the QN instead of Q of pseudo divide-by-2/3 prescaler) so that the delay decreases from tD\_Q to tD\_QN. The operation mode of the proposed circuit is as follows:

- 1. When modulus control MC=1, the pseudo divide-by-2/3 prescaler accomplishes seven times of divide-by-2 operation and one time of divide-by-3 operation in a cycle. Therefore the circuit operates in divide-by-17 mode.

- 2. When MC=0, the pseudo divide-by-2/3 prescaler accomplishes only divide-by-2 operations in a cycle. Therefore the whole circuit operates in divide-by-16 mode. In theory, it is difficult to estimate which path decides the minimum working period. The optimized design is to make the critical path #1 approximately equal to half length of critical path #2.

Therefore the minimum working period of conventional divide-by-16/17 prescaler can

A Peer Revieved Open Access International Journal

www.ijiemr.org

be written as Tmin,con = (1/2) tD\_Q,DFF1 + tD\_QN,DFF2 + tD ,NAND +t'setup, DFF0 (1) These two critical paths should be optimized to achieve high speed which is a great challenge for designers.

The critical path is optimized by replacing the OR and NAND gate by AND gate in the proposed

system. This reduces the propagation delay which in turn decreases the minimum working period of the prescaler. The reduction of working period in proposed system is achieved by decreasing its delay. The delay is decreased by adopting a pseudo divide-by-2/3 prescaler and changing the interconnection between the TSPC D flip-flops.

### III. PROPOSED DIVIDE-BY-16/17 DUAL MODULUS PRESCALER

The maximum working frequency of the proposed system is decided by its divide-by-17 operation mode. The key operation in

divide-by 17 mode is the divide-by-3 operation of pseudo divide-by-2/3 prescaler.

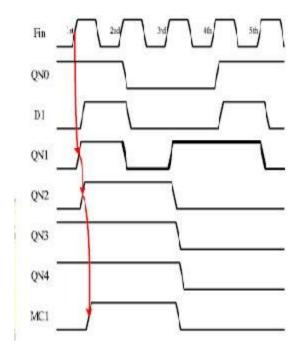

Fig.4. Timing diagram of proposed divideby- 16/17 prescaler

Fig.4. shows the timing diagram of divideby- 3 operation of the proposed circuit. The operation of the timing diagram is as follows:

- i. In the first rising edge of Fin, QN1 and QN2 switch to high. So MC1 switches to high and holds for two periods.

- ii. In the second rising edge of Fin, QN0 andD1 switch to low and hold for two periods.

A Peer Revieved Open Access International Journal

www.ijiemr.org

iii. In the third rising edge, QN1 switches to high and holds for two periods. From the second to fifth rising edge of Fin, DFF1 outputs a divide-by-3 signal in node QN1 pseudo divide-by-2/3 and prescaler accomplishes a divide-by-3 operation. After this, the pseudo divide-by- 2/3 prescaler will carry out seven times divide-by-2 operation. A divide-by-17 signal is obtained in node Fout. The minimum working period of the proposed prescaler can be written as Tmin,pro (1/2)tD\_QN,DFF1 tD\_QN,DFF2 + t"setup, DFF0 operation of dual modulus prescaler. When MC=1, dual modulus prescaler divides the frequency by 17. When MC=0, it operates in divide-by-16 Here the delay is calculated in simulation which is in the range of  $\mu$ s. (2) Where tD\_QN,DFF1 is the propagation delay from clk ON1 of to DFF1. tD\_QN,DFF2 is the propagation delay from clk to QN2 of DFF2. t"setup, DFF0 is the setup time with absorbed AND1 gate. From equations (1) and (2), it is clear that the minimum working period of the proposed divideby- 16/17 prescaler is reduced by half an inverter's delay and half a NOR gates delay. Therefore the difference in delay

between conventional and proposed divideby-16/17 prescaler circuit can be written as

Tmin,con-Tmin,pro

$$\approx$$

TD\_NOR + TD\_INV

By adopting a Pseudo divide-by-2/3 prescaler, the minimum working period is reduced by half a NOR gate's delay. By changing the connection of TSPC DFF's, the minimum working period is further reduced by half an inverter's delay. and half an inverter's delay is decreased by adopting pseudo divide-by-2/3 prescaler and by changing the connections between TSPC

#### RELATED WORK

D flip flops.

As far as, the proposed system was only concerned with the delay and speed. My future work is to design the prescaler with low power consumption and to increase the frequency range up to 12 GHz and to further implement it in the fractional N-PLL frequency synthesizer to achieve accurate phase and frequency comparisons.

#### IV. SIMULATION RESULTS

A Peer Revieved Open Access International Journal

www.ijiemr.org

operation of dual modulus prescaler. When MC=1, dual modulus prescaler divides the clock frequency by 17. When MC=0, it operates in divide-by-16 Here the delay is calculated in simulation which is in the range of μs.

Fig.5. Output of existing system

The dual modulus prescaler was simulated using 250 nm CMOS technology.Fig.5 shows the

output of existing system. It also reveals the

Fig.6 shows the output of proposed system. The operating frequency range can be simulated up to 5.8 GHz. The delay calculated in the simulation is found to be in the range of ns which is smaller compared to the existing system. The minimum working period is reduced in the proposed system is 3.48 secs. Therefore, this guarantees that the working period of the proposed prescaler is reduced than the existing conventional system.

#### V. CONCLUSION

A high speed dual modulus prescaler has been designed using 250 nm CMOS technology. Pseudo divide-by-2/3 prescaler reduces the minimum working period by half a NOR gate's delay. By changing the connection between TSPC D Flip flops, its minimum working period is reduced by about half an inverter's delay. Therefore the speed of the proposed system is enhanced by adopting pseudo divide-by-2/3 prescaler and by changing its interconnection between the flip flops. The operating frequency is also simulated to be up to 5.8 GHz with low delay.

Fig.6. Output of proposed system

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### REFERENCES

1. C.-Y. Yang, G.-K. Dehng, J.-M. Hsu, and S.-I. Liu,(Oct. 1998) "New dynamic flip-flops for high-speed dualmodulus prescaler," IEEE J. Solid-State Circuits, vol. 33,10, pp. 1568–1571.

2. H. Shin, (Jan. 2012.) "A 1-V TSPC dual modulus prescaler with speed scalability using forward body biasing in 0.18 μm CMOS," IEICE Trans. Electron., vol. E95-C, no. 6,pp. 1121–1124,

3. J. M. Rabaey, A. Chandrakasan, and B. Nikolic, (2003) Digital Integrated Circuits: A Design Perspective, 2<sup>nd</sup> ed. New York, NY, USA: Prentice Hall, pp.350–352. 4. J. Yuan and C. Svensson,(Feb. 1989) "Highspeed CMOS circuit technique," IEEE J. Solid-State Circuits, vol. 24, no. 1, pp. 62–70.

#### **AUTHOR 1:-**

\*Ch.Priyanka completed her B-tech in Supraja Institute of Technology & Sciences. in 2014 and completed M-Tech in Vaagdevi college of Engineering.

#### **AUTHOR 2:-**

\*\* Mr.K.Thirupathi is working as Assistant. professor in Dept of ECE, Vaagdevi College of Engineering.

#### **AUTHOR 3:-**

\*\*\*Mr.M.Devadas is working as Assistant.professor in Dept of ECE, Vaagdevi College of Engineering.